This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

# SP97508

# 110MHz 8-BIT FLASH ADC

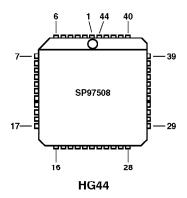

The SP97508 is an 8-bit flash ECL analog-to-digital converter. It incorporates 256 individual comparators, a reference chain and a full D-type output latch. The ADC is capable of sampling at 100MHz with full (Nyquist) analog bandwidth and has an excellent dynamic performance. A conventional unity mark/space ratio clock can be used and the output data can be programmed for true or inverse binary and twos' complement coding.

#### **FEATURES**

- Full Scale Input Bandwidth 120MHz (3dB)

- No Missing Codes

- Production Tested with 30MHz Analog Input

- Low Input Capacitance: 32pF (Max.)

- No External Sample and Hold Needed

- Low Power Consumption: 1.4W (Typ.)

- True/Inverse Binary and Twos' Complement Coding

- Operating Temperature Range: -40°C to +85°C

#### **APPLICATIONS**

- Radar Video Digitising

- Instrumentation

- Nucleonics

- Studio Quality Video

# ORDERING INFORMATION

SP97508B HG (Industrial - J-Lead Quad Cerpac) SP97508B AC (Industrial - Pin Grid Array)

#### **ABSOLUTE MAXIMUM RATINGS**

| Power supply VEE                    | 0V to -7V      |

|-------------------------------------|----------------|

| Analog input V <sub>IN</sub>        | +0.5V to VEE   |

| Reference voltages Vвт, Vвм, Vвв    | +0.5V to VEE   |

| Reference range VRT - VRB           | 2.5V           |

| Digital inputs CLK, CLK, MINV, LINV | +0.5V to -4V   |

| MidRef input current IVRM           | -10mA to +10mA |

| Digital output current lo           | 0 to -20mA     |

| Voltage between AGND and DGND       | -50mV to +50mV |

| Voltage between AVEE and DVEE       | -50mV to +50mV |

|                                     |                |

# THERMAL CHARACTERISTICS

| Storage temperatu  | -65°C to +150°C |        |

|--------------------|-----------------|--------|

| Max. junction oper | +175°C          |        |

| Lead temperature   | (soldering 60s) | 300°C  |

| SP97508B HG        | hetaJA          | 46°C/W |

|                    | θις             | 11°C/W |

| SP97508B AC        | θμα             | 40°C/W |

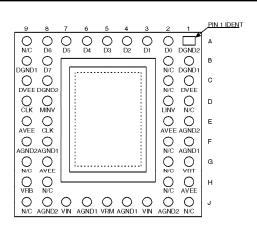

#### AC46

| Pin | Function | Pin | Function    | Pin | Function        |

|-----|----------|-----|-------------|-----|-----------------|

| 1   | NC       | 16  | DGND        | 31  | AGND            |

| 2   | LINV     | 17  | DGND        | 32  | VIN             |

| 3   | NC       | 18  | NC          | 33  | AGND            |

| 4   | DVEE     | 19  | DVEE        | 34  | V <sub>RM</sub> |

| 5   | DGND     | 20  | MINV        | 35  | AGND            |

| 6   | DGND     | 21  | NC_         | 36  | Vin             |

| 7   | NC       | 22  | CLK         | 37  | AGND            |

| 8   | D0 LSB   | 23  | CLK         | 38  | NC              |

| 9   | D1       | 24  | NC          | 39  | NC              |

| 10  | D2       | 25  | <b>V</b> RB | 40  | NC              |

| 11  | D3       | 26  | AVEE        | 41  | AVEE            |

| 12  | D4       | 27  | AVEE        | 42  | AVEE            |

| 13  | D5       | 28  | NC          | 43  | NC              |

| 14  | D6       | 29  | NC          | 44  | <b>V</b> RT     |

| 15  | D7 MSB   | 30  | NC          |     |                 |

Fig.1 Pin connections - top view

Fig.2 SP97508 functional block diagram

# PIN DESCRIPTIONS (Pin numbers refer to HG44 package only)

| Pin                     | Function                                                                                                                                                                             |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVEE                    | Analog Vee, -5.2V (typ.).                                                                                                                                                            |

| LINV<br>DVEE            | Input pin for polarity inversion of output data bits D0 to D6 (see Table 1). Digital VEE, -5.2V (typ.).                                                                              |

| DGND<br>D0-D7           | Digital ground, separated from the analog ground (AGND). data output pins, ECL levels, D7 = MSB, D0 = LSB. External pulldown resistors are required, e.g. 68αΩ to DV <sub>==</sub> . |

| MINV                    | Input pin for polarity inversion of D7 (MSB) (see Table 1). ECL '0' level is held when MINV is open circuit.                                                                         |

| CLK<br>CLK              | Clock input pin, ECL levels. Analog input signal, V <sub>IN</sub> , acquired on rising edge (see Fig.8).<br>Inverse clock input pin , ECL levels.                                    |

| <b>V</b> RB             | Reference voltage (bottom), -2V (typ).                                                                                                                                               |

| AGND<br>V <sub>IN</sub> | Analog ground.<br>Analog input, range (Vrt - Vrb) p-p.                                                                                                                               |

| VRM                     | Midpoint of the reference voltage; can be used for linearity adjustment.                                                                                                             |

| V <sub>RT</sub><br>NC   | Reference voltage (top), 0V (typ.).<br>Not Connected. Pins 1 and 18 should be connected to DGND, all others AGND.                                                                    |

# **RECOMMENDED OPERATING CONDITIONS**

| Supply voltage Reference (VRT) Reference (VRR) | -5.2V ± 0.25V<br>0V ± 0.1V<br>-2.0V + 0.2V | AGND to DGND Analog input Output load | 0mV ± 50mV<br>2V p-p max.<br>680Q to -5 2V |

|------------------------------------------------|--------------------------------------------|---------------------------------------|--------------------------------------------|

| Reference (VRB) AVEE to DVEE                   | $-2.0V \pm 0.2V$<br>0mV $\pm 50$ mV        | Output load                           | 680Ω to -5.2V                              |

# **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):  $T_{amb} = 25^{\circ}C$ ,  $V_{EE} = -5.2V$ ,  $V_{RT} = 0V$ ,  $V_{RB} = -2V$ , full temperature range = -40°C to +85°C

| Ob and should be                                | Symbol            | Temp       | Test   | st Value |            | Value      |                          | 0 - 1111                                       |

|-------------------------------------------------|-------------------|------------|--------|----------|------------|------------|--------------------------|------------------------------------------------|

| Characteristic                                  | Symbol            | (°C)       | level  | Min.     | Тур.       | Max.       | Units                    | Conditions                                     |

| Power Supply                                    |                   |            |        |          |            |            |                          |                                                |

| Supply current                                  | lee               | 25         | 1      | 180      | 270        | 300        | mA                       |                                                |

| A                                               |                   | Full       | 4      | 165      |            | 310        | mA                       |                                                |

| Analog Input Input bias current                 | lin               | ٥٢         |        |          | 450        | 005        |                          |                                                |

| Imput bias current                              | IIN               | 25<br>Full | 1<br>4 | 80<br>50 | 150        | 285<br>350 | μ <b>Α</b><br>μ <b>Α</b> |                                                |

| Input bandwidth (3dB)                           |                   | 25         | 4      | 30       | 120        | 350        | μΑ<br>MHz                |                                                |

| Input capacitance                               | Cin               | 25         | 4      |          | 29         | 32         | pF                       | V <sub>IN</sub> = 0V                           |

| Input resistance                                | Rin               | 25         | 4      |          | 75         |            | kΩ                       | V <sub>IN</sub> = 0V                           |

| Reference Chain                                 |                   |            |        |          |            |            |                          |                                                |

| Ladder resistance                               | RR                | 25         | 1      | 90       | 105        | 135        | Ω                        |                                                |

| Ladder offset (top & bottom)                    | V <sub>RT/B</sub> | Full<br>25 | 4<br>3 | 70       | 7.5        | 155        | Ω<br>mV                  |                                                |

| Clock Input                                     | V H I/B           | 25         | 3      |          | 7.5        |            | IIIV                     | I/P voltage swing = 1Vp-p                      |

| Logic '1' voltage                               | VIH               | 25         | 4      | -3.05    |            | DGND       | V                        | Voltage swillg = TVP-P                         |

| Logic '0' voltage                               | Vı∟               | 25         | 4      | -3.85    |            | -0.8       | V                        |                                                |

| Logic '1' current                               | lін               | 25         | 1      |          |            | 380        | μΑ                       | V <sub>IH</sub> = -0.8V                        |

|                                                 |                   | Full       | 4      | 310      | 360        | 390        | μΑ                       | VIH = -0.8V                                    |

| Logic '0' current                               | lı∟               | 25         | 4      |          | 000        | 280        | μΑ                       | V <sub>IL</sub> = -1.8V                        |

| Min. pulse width (high)                         |                   | Full<br>25 | 4      | 220      | 260<br>3   | 290        | μA<br>ns                 | V <sub>IL</sub> = -1.8V                        |

| Min. pulse width (low)                          |                   | 25         | 4      |          | 2.3        |            | ns                       |                                                |

| Digital Outputs                                 |                   | 20         |        |          | 2.0        |            | 110                      |                                                |

| Logic '1' voltage                               | <b>V</b> он       | 25         | 1      | -0.90    | -0.83      |            | ٧                        | $R_L = 680\Omega$ to DVEE                      |

|                                                 | <b>.</b>          | Full       | 4      | -1.00    |            |            | V                        |                                                |

| Logic '0' voltage                               | <b>V</b> ol       | 25         | 4      |          | -1.80      | -1.90      | V                        | $R_L = 680\Omega$ to $DV_{EE}$                 |

| Switching Performance                           |                   | Full       | 4      |          |            | -1.65      | V                        |                                                |

| Max. conversion rate                            | fc                | 25         | 4      | 110      |            |            | MHz                      | fin = 50MHz at FS                              |

| Aperture delay                                  | tad               | 25         | 5      | 110      | 1.9        |            | ns                       | 111N = 301VII 12 At 1 3                        |

| Aperture uncertainty                            | tau               | 25         | 4      |          | 30         |            | ps rms                   |                                                |

| Output data delay                               | td                | 25         | 4      |          | 2.9        |            | ns                       | $R_L = 680\Omega$ to $DV_{EE}$                 |

| Output data rise time                           | tr                | 25         | 4      |          | 2.0        |            | ns                       | $R_L = 680\Omega$ to DVEE                      |

| Output data fall time                           | t <sub>f</sub>    | 25         | 4      |          | 1.6        |            | ns                       | $R_L = 680\Omega$ to DVEE                      |

| Output data time skew Static Performance        | ts                | 25         | 4      |          | 0.4        |            | ns                       | $R_L = 680\Omega$ to DVEE                      |

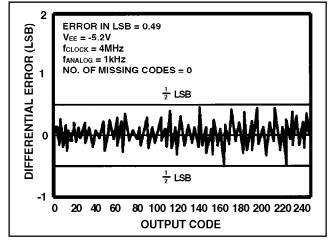

| Differential non-linearity                      | DNL               | 25         | 1      | -0.85    | ±0.5       | 0.85       | LSB                      | fc = 4MHz, fin = 1kHz ramp<br>No missing codes |

| ,                                               |                   | Full       | 4      | -1.0     | 0.0        | 1.0        | LSB                      | No missing codes                               |

| Integral non-linearity                          | INL               | 25         | 1      | -1.4     |            | 1.3        | LSB                      |                                                |

|                                                 |                   | Full       | 4      | -1.8     |            | 1.6        | LSB                      |                                                |

| Missing codes                                   |                   | 25         | 1      |          | missing c  |            | 0/ 50                    | Guaranteed                                     |

| Gain error Offset error                         |                   | 25<br>25   | 1 1    | -1.5     |            | 1.5        | %FS<br>mV                |                                                |

| Dynamic Performance                             |                   | 25         | '      | -15      |            | 0          | 1110                     | fc = 100MHz                                    |

| Transient response (rise)                       |                   | 25         | 4      |          | 2.4        |            | ns                       | 1 fin = 50MHz                                  |

| Transient response (fall)                       |                   | 25         | 4      |          | 2.1        |            | ns                       | square wave at FS                              |

| Slew rate                                       |                   |            | 4      |          | 1.0        |            | V/ns                     |                                                |

| Differential non-linearity                      | DNL               | 25         | 1      | -0.9     |            | 1.4        | LSB                      | fin = 30MHz                                    |

| Integral non-linearity<br>Signal-to-noise ratio | INL<br>SNR        | 25<br>25   | 1 4    | -3.0     | 45.8       | 3.0        | LSB<br>dB                | sinewave at FS fin = 1MHz at FS                |

| Olghar to Holse ratio                           | ONT               | 25         | 1      | 41       | 44.5       |            | dB<br>dB                 | fin = 10MHz at FS                              |

|                                                 |                   | 25         | 4      | -        | 39.0       |            | dB                       | fin = 30MHz at FS                              |

| Total harmonic distortion                       | THD               | 25         | 4      |          | 53.5       |            | dBc                      | fin = 1MHz at FS                               |

|                                                 |                   | 25         | 1      | 46       | 48.5       |            | dBc                      | fin = 10MHz at FS                              |

| Effective number of hits                        | ENICOR            | 25         | 4      |          | 40.4       |            | dBc                      | fin = 30MHz at FS                              |

| Effective number of bits                        | ENCOB             | 25         | 4      | 6.5      | 7.3        |            | bits                     | fin = 1MHz at FS                               |

|                                                 |                   | 25<br>25   | 1<br>4 | 6.5      | 7.1<br>6.2 |            | bits<br>bits             | fin = 10MHz at FS<br>fin = 30MHz at FS         |

| Bit error rate                                  | BER               | 25         | 4      |          | 1 in 10°   |            | 210                      | fin = 50MHz at ₹ FS                            |

|                                                 |                   | ı          |        |          | ı · · ў    |            |                          |                                                |

# ELECTRICAL CHARACTERISTICS DEFINITIONS Analog Bandwidth

The analog input frequency at which the spectral power of the fundamental frequency, as determined by Fast Fourier Transform analysis is 3dB down on the DC level.

Aperture Delay

The delay between the rising edge of the CLOCK signal and the instant at which the analog input is sampled.

#### **Aperture Jitter**

The sample-to-sample variation in aperture delay. Bit Error Rate (BER)

The number of spurious code errors produced for any given input sinewave frequency at a given clock frequency. In this case it is the number of codes occuring outside the histogram cusp for a <sup>3</sup>/<sub>4</sub> FS sinewave.

#### **Differential Non-Linearity (DNL)**

The deviation of any code width from ideal 1LSB step.

#### **Effective Number of Bits (ENOB)**

This is a measure of the device's dynamic performance and may be obtained from the SNR or form a sine wave curve fit test, according to the following expressions:

ENOB =

$$\frac{\text{SNR-1.76}}{6.02}$$

or ENOB = N-log<sub>2</sub>  $\frac{\text{rms error (actual)}}{\text{rms error (ideal)}}$

where N is the conversion resolution and the rms error is the deviation of the output from an input sine wave.

#### Integral Non-Linearity (INL)

The deviation of the centre of each code from a reference line which has been determined by a least squares curve fit. **Output Delay**

The delay between the 50% point of the falling edge of the clock signal and the 50% point of any data output change.

#### Reference Ladder Offset

The voltage error at the ends of the resistor chain caused by the end terminations, the lead frame and the bond wire. Signal-to-Noise Ratio (SNR)

The ratio of the RMS signal amplitude to the RMS value of 'noise' which is defined as the sum of all other spectral components, including harmonics but excluding DC with a full scale analog input signal.

#### **Total Harmonic Distortion (THD)**

The RMS value of all the harmonics compared with the RMS value of the fundamental.

# **Transient Response**

The time required by the outputs to move from 10(90)% to 90(10)% of the full scale range.

# Test Levels

Level 1 - 100% production tested at 25°C

**Level 2** - 100% production tested at 25°C and sample tested at specified temperatures

Level 3 - Sample tested only

**Level 4** - Parameter is guaranteed by characterisation or design

Level 5 - Parameter is a typical value only

# **APPLICATION NOTES**

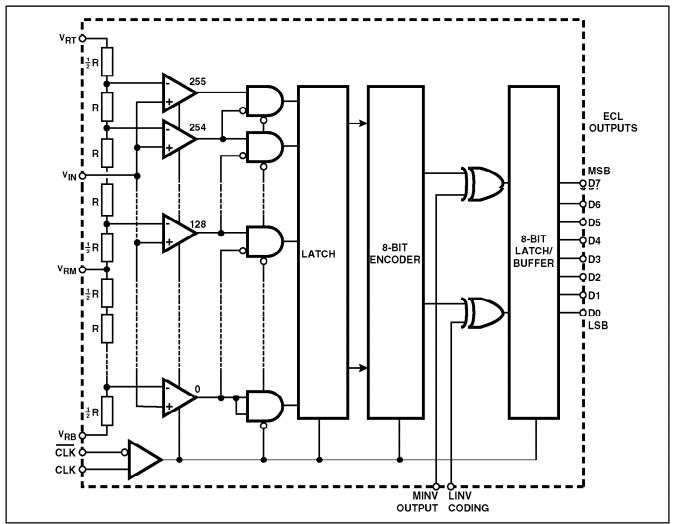

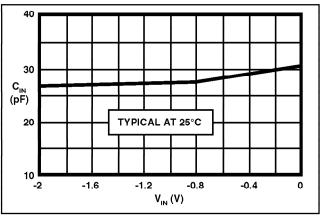

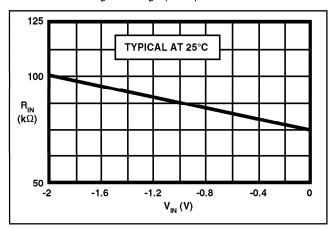

#### Analog Input (Figs.3, 4 and 5)

The maximum amplitude and offset of the input is defined by the reference voltages ( $V_{\rm RB}$  to  $V_{\rm RT}$ ). The optimum input is 2V p-p with a DC offset of -1V. The analog input circuit of the SP97508 consists of 256 buffered comparator inputs, as shown in Fig. 3.

The internal buffering to the device results in the typical input characteristics of Figs. 4 and 5. The dependence of input

capacitance on voltage level is typical of flash converters and so requires that the analog input is driven from a low impedance source such as the SL9999.

Failure to drive the input capacitance properly causes increased levels of harmonic distortion, most noticeable in the second harmonic.

Fig.3 Analog input

Fig.4 Analog input capacitance

Fig.5 Analog input resistance (AC)

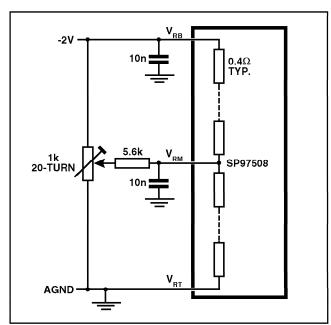

#### Reference Pins (Fig. 6)

Between VRT and VRB there are 256 series resistors forming the reference chain. The total resistance may be between  $90\Omega$  and  $120\Omega$ . A mid-reference pin (VRM) is also provided as an option for precision setting of integral linearity. Both VRM and VRB should be adequately decoupled to analog ground. For optimum performance, VRT is connected directly to analog ground and VRB is driven from a -2V DC supply. For precise reference setting, this supply should be adjustable by  $\pm 0.2V$ .

Fig.6 Reference connections

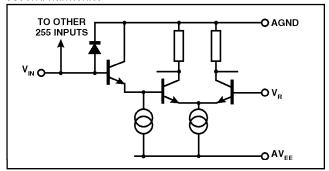

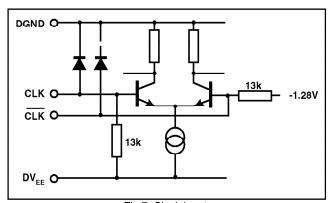

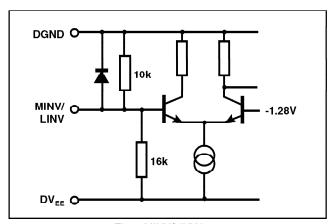

Fig.7 Clock inputs

# Clock Inputs CLK and CLK (Figs. 7 and 8)

The SP97508 can be driven from either differential or single-ended ECL clocks. In either mode, the clock lines should be terminated with the line's characteristic impedance close to the device clock pins. For full 100MHz operation, a conventional unity mark/space ratio clock can be used.

Single-ended drive can be simply provided by adding a 1nF chip or encapsulated chip capacitor from the CLK pin to DGND. The CLK pin will then self-bias at -1.28V, which is the mid-threshold for ECL. The device can then be clocked by an ECL signal into the CLK input.

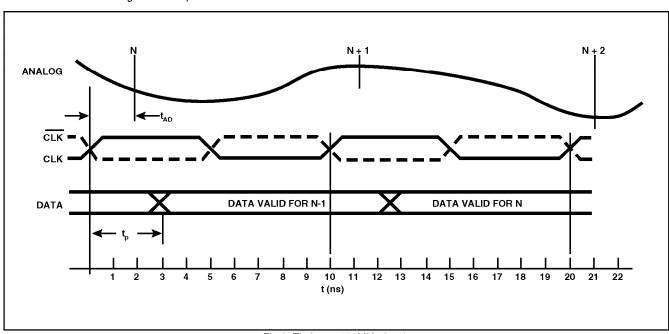

# Timing (Fig.8)

The analog input is acquired by the device shortly after the rising edge of the CLK signal. The internal latch causes a one cycle delay, hence the output data is valid one clock cycle after the acquisition of the analog signal.

The output data is further delayed by the clock-to-output delay (to = 2.9ns typ.). This gives the advantage that the same timing and phase of the SP97508 CLK signal can be used to acquire the output data.

Fig.8 Timing at 100MHz (typ.)

#### Output Coding (Table 1 and Fig.9)

With MINV and LINV left open circuit, the output will be coded in standard binary with all 1s code corresponding to the most positive input  $V_{\text{IN}}=V_{\text{RT}}=0V$ .

An inverse binary output can be provided by connecting both MINV and LINV to ground.

Two's complement coding (inverted MSB) can be provided by connecting only the MINV pin to ground and inverse two's complement coding can be achieved by connecting only the LINV pin to ground.

|     | Binary         | Inv 2s' comp.  | 2s' comp.      | Inv binary     |

|-----|----------------|----------------|----------------|----------------|

| VIN | MINV = O/C (0) | MINV = O/C (0) | MINV = GND (1) | MINV = GND (1) |

|     | LINV = O/C (0) | LINV = GND (1) | LINV = O/C (0) | LINV = GND (1) |

| ŌΛ  | 111 11         | 100 00         | 011 11         | 000 00         |

|     | 111 10         | 100 01         | 011 10         | 000 01         |

|     | -              | -              | -              | -              |

|     | -              | -              | -              | -              |

|     | -              | -              | -              | -              |

|     | 100 00         | 111 11         | 000 00         | 011 11         |

|     | 011 11         | 000 00         | 111 11         | 100 00         |

|     | -              | -              | -              | -              |

|     | -              | -              | -              | -              |

|     | -              | -              | -              | -              |

|     | 000 01         | 011 10         | 100 01         | 111 10         |

| -2V | 000 00         | 011 11         | 100 00         | 111 11         |

Table 1

Fig.9 MINV/LINV input

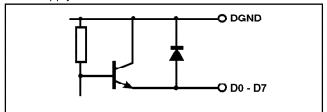

#### 8-Bit ECL Outputs (Fig.10)

The outputs are standard ECL open emitters and therefore require pull-down resistors connected from the outputs to -5.2V or -2V digital supply. Single in-line resistors of value  $680\Omega$  to  $1k\Omega$  are recommended for termination to DVEE. The outputs are capable of driving  $200\Omega$  terminations connected to a -2V supply.

Fig.10 Digital output

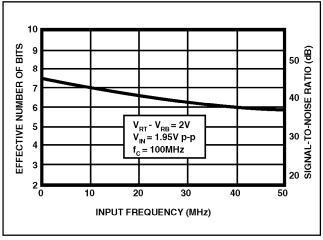

#### TYPICAL PERFORMANCE CHARACTERISTICS

Fig.11 Static differential linearity in LSB: typical production device

Fig.12 Effective number of bits (ENOB) and signal-to-noise ratio (SNR) v. input frequency

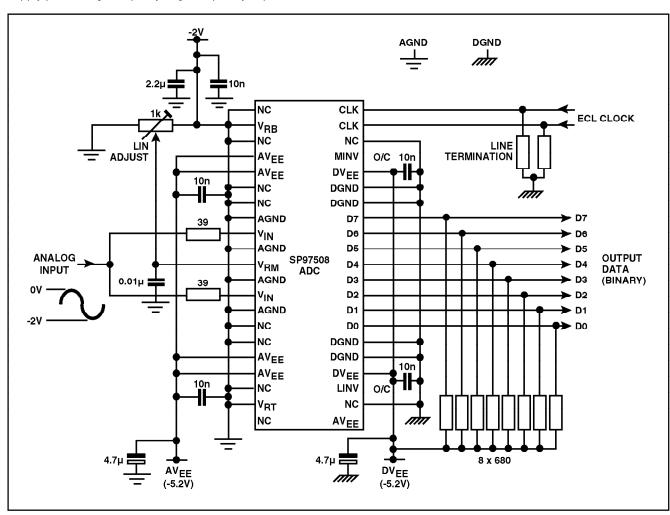

#### CIRCUIT BOARD CONSTRUCTION

As with most PCB construction for analog-to-digital conversion, the best performance from the SP97508 can be achieved by separating the ground plane into two sections: analog ground (AGND), and digital ground (DGND). This aids the device performance by reducing the degree of noise due to digital switching fed back to the analog section of the converter.

The digital noise is produced mainly by the ECL binary outputs, which, ideally, should be terminated by a  $680\Omega$  load to the -5.2V digital supply, DVEE.

The device supplies are also a source of digital feedback, as they can be modulated by the digital output current. It is wise, therefore, to decouple the SP97508 close to the device supply pins with good quality, high frequency capacitors.

#### **Notes on Construction**

- Use split analog and digital ground planes connected together close to the device. Do not run the analog input next to the clock or data lines.

- All NC pins must be grounded: connect pins 1 and 18 to DGND, all others to AGND.

- 3. Connect digital and analog supplies together at a point on the PCB away from the device.

- 4. Use 10nF capacitors for supply decoupling.

- 5. Use stripline techniques for siginal paths longer than 5cm (2 inches)

- Use 4.7μF electrolytic capacitors to decouple the -5.2V VEE supplies

Fig.13 Test and Application circuit

# HEADQUARTERS OPERATIONS

# GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom.

Tel: (0793) 518000 Fax: (0793) 518411

Fax: (408) 438 5576

#### **GEC PLESSEY SEMICONDUCTORS**

P.O. Box 660017 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel: (408) 438 2900

#### **CUSTOMER SERVICE CENTRES**

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax : (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel (408) 438 2900 Fax: (408) 438 7023.

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- **SWEDEN** Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- TAIWAN, ROC Taipei Tel: 886 2 5461260. Fax: 886 2 7190260

- UK, EIRE, DENMARK, FINLAND & NORWAY

Swindon Tel: (0793) 518510 Fax: (0793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1994 Publication No. DS2092 Issue No. 2.3 July 1994

TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not possible in the products are used in the products are used in the products are used in the products are not suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.